Heterogeneous Integration Fabric

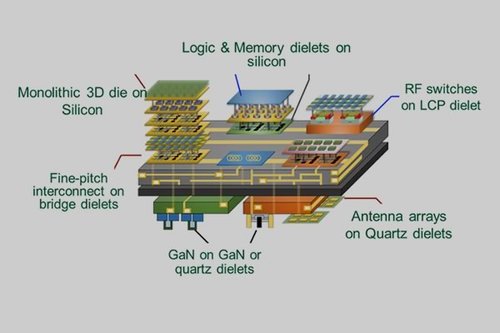

Theme 3 (Multi-function Heterogeneous Fabric), proposes a radical departure from the current roadmap of board level integration of heterogeneous ICs and targets functional diversification of future micro-systems by introducing the HeterogeneoUs faBric (the HUB) where fine-pitch micro-aligned integration of functionally diverse dielets will be enabled on rigid and/or flexible substrates.

Each technologically and functionally diverse chip will be integrated on the substrate thus enabling massive integration as well as reuse of intellectual property (IP) blocks. Dielets will comprise of logic and memory chips (sourced from Themes 1 and 2 of ASCENT) as well as RF blocks, passives and DC-DC power converters that will be developed as a part of Theme 3 (including component-off-the-shelf, COTS). Combine the best of chip technologies and design IPs into a heterogeneous microsystem by tiling dielets together on an ultra-dense interconnect fabric.

Combine the best of chip technologies and design IPs into a heterogeneous microsystem by tiling dielets together on an ultra-dense interconnect fabric.

The Theme will develop key component and platform technologies, circuit macros as well as end-to-end, vertically-integrated tools chains that will allow high-performance, energy-efficient functionally-diverse designs. This Theme will seek revolutionary solutions to the exponentially increasing challenges in power delivery, signal integrity, thermal management and electromagnetic/RF interferences that naturally come with terra-scale integration of logic, memory and analog nano-components.

ASCENT will strategically leverage innovations in materials for logic, memory and analog devices and seek new packaging paradigm to provide superior power-performance-reliability-cost in smaller volume, with higher security through smart shielding, with efficient power management by fine-grain integration of passives, and enhanced communication bandwidth by package level implementation of waveguides.

Affiliated Investigators

Muhannad S. Bakir

Electrical and Computer Engineering Georgia Tech

Kenneth Goodson

Mechanical Engineering and Materials Science & Engineering Stanford

Subramanian Iyer

Electrical and Computer Engineering UC Los Angeles

Stacia Keller

Electrical and Computer Engineering UC Santa Barbara

Madhavan Swaminathan

Electrical and Computer Engineering Georgia Tech