Vertical CMOS

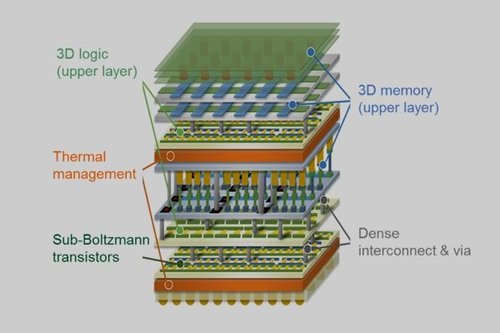

Theme 1 (Vertical CMOS), addresses the fundamental challenges encountered during implementation of monolithic sequential 3D integrated circuits with multiple inter-leaved layers of logic and memory when stacked atop each other.

This theme is developing novel low temperature synthesis routes for high mobility n and p–type semiconductors that can used for low thermal budget fabrication of high-performance complementary transistors in upper layers to support 3D logic.

Novel transistors fabricated entirely in the BEOL process will support not only 3D DRAM cell stacking structure similar to 3D-NAND, but also can enable 3D logic.

High density 3D cross-point phase change memory has been commercially introduced to improve memory bottleneck, but need fundamental breakthroughs in abrupt threshold selectors to further improve memory array efficiency. This theme explores new designer materials to make breakhrough advances in selector devices for 3D cross-point memories. Vertical RRAM development is also limited by lack of a good selector that can reside on pillar sidewalls, which is addressed in this theme.

Enable hyper scaling by stacking logic and memory layers in the vertical dimension with ultra-dense connectivity.

Fine grained thermal management in ultra-high density 3D Enable hyper scaling by stacking logic and memory layers in the vertical dimension with ultra-dense connectivity circuits is of paramount importance. This theme explores hybrid nanostructures with enhanced thermal conductivity for mitigating transistor self-heating in the upper layers.Local and global interconnect scaling is a major roadblock for both traditional and vertical CMOS. This theme explores low temperature selective ALD of non-Cu metal solutions and selective ALD of work-function engineered metal silicides for transistor contacts. Exploratory 3D Dirac semi-metals with anisotropic Fermi surfaces are also explored to address scaling of wires to atomic dimensions. The researchers also explore SAM (Self-Assembled Monolayers) as candidates for ultra-scaled diffusion barriers in interconnects at advanced nodes.

The theme finally targets demonstration of steep slope transistors operating at extremely low voltages by exploiting collective excitations in functional oxides such as insulator-to-metal and ferroelectric phase transitions that give rise to negative differential resistance (NDR) and negative differential capacitance (NDC), respectively.